Designing the computational architecture of the future

ASU researchers to lead $17M effort to expand the capabilities and energy efficiency of computing technologies

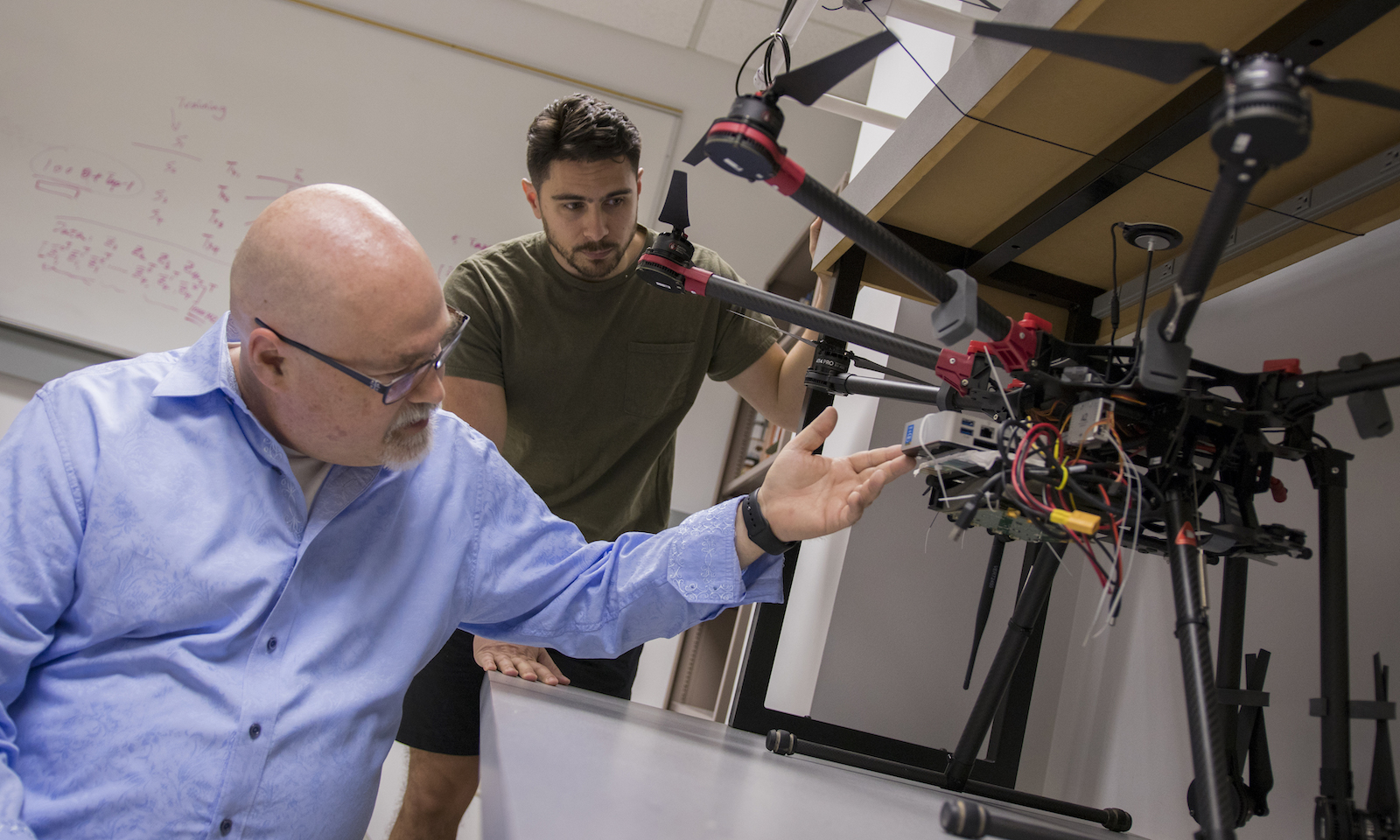

Under the new Electronics Resurgence Initiative research program administered by an agency of the U.S. Department of Defense, Ira A. Fulton Schools of Engineering Professor Daniel Bliss (foreground) and his research team will develop a framework for designing and building advanced heterogeneous computing platforms that enable rapid development of multi-application systems. Pictured with Bliss is Richard Gutierrez, a recent electrical engineering doctoral graduate. Photographer: Marco-Alexis Chaira/ASU

As advances in 21st-century engineering and science increase in number and rapidity, the progress only arouses stronger ambitions to achieve even bigger discoveries and broader technological capabilities.

Many of those aspirations are constrained by the limitations of current computing technologies, says Daniel Bliss, an associate professor of electrical, computer and energy engineering in Arizona State University’s Ira A. Fulton Schools of Engineering.

“I am always computation hungry. I’m interested in taking steps forward on a lot of advanced communications, radar and medical systems, but I never have the computational ability I need,” says Bliss, a systems engineer.

That’s why he is eager to begin work on what for him is a dream endeavor. Bliss is leading one of many research efforts being pursued under the new national Electronics Resurgence Initiative headed by the U.S. Defense Advanced Research Projects Agency, commonly known as DARPA, an agency of the Department of Defense.

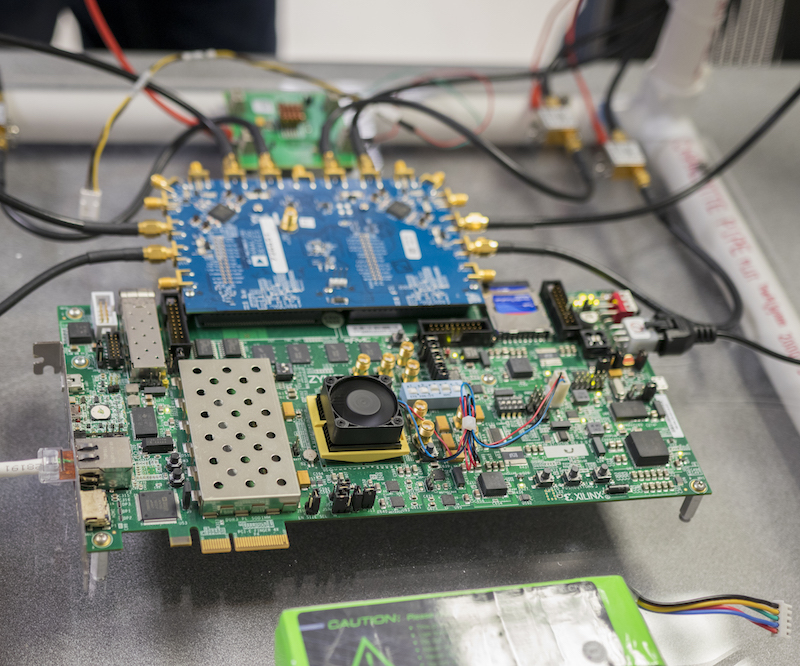

Professor Daniel Bliss and his team use current heterogenous processor technology, like the Zynq Multiprocessor System on Chip shown here, for advanced electronic applications. As part of the recently announced Electronics Resurgence Initiative, the team will create a conceptual framework, software tools and integrated circuits for new, more power-efficient computer processing architectures. Photographer: Marco-Alexis Chaira/ASU

Under the direction of DARPA’s Microsystems Technology Office, the initiative’s mission is to spark innovative solutions to overcome obstacles that have impeded significant evolution in microelectronic systems — including computing systems.

More specifically, the goals of the DARPA initiative’s Domain-Specific System on Chip (DSSoC) program align precisely with the aims of ASU’s Center for Wireless Information Systems and Computational Architectures, which Bliss directs.

The initiative’s directives “are all about exactly what we want to do,” Bliss says. “The bottom line is to help satisfy that hunger for greater computational power that is required by sophisticated signal processing applications.”

Bliss’ team will build a new framework to push development of the next generation of high-performance embedded heterogeneous computer processors that are more capable, more power efficient and easier to use.

The team’s focus will be on computer architecture, specifically creating a framework that simplifies the development of new heterogeneous processors with advanced functionalities and streamlines the use of these processors.

Heterogeneous processors use multiple processors of different kinds on one integrated circuit. Adding various types of coprocessors with specialized capabilities to perform specific computing tasks boosts a system’s performance and energy efficiency.

However, heterogeneous processors are notoriously difficult to program, so Bliss’ team will provide software tools and on-chip intelligence to dramatically simplify implementation.

A key part of DARPA’s objective is to engage the electronics industry and commercial enterprises in the ERI’s research projects. So, Bliss and his ASU team will be working not only with fellow researchers at Carnegie Mellon University, the University of Arizona and the University of Michigan, but also with Arm Limited, a semiconductor intellectual property company, EpiSys Science Inc. and General Dynamics Mission Systems.

Professor Chaitali Chakrabarti and Assistant Professors John Brunhaver and Umit Ogras — all faculty in ASU’s School of Electrical, Computer and Energy Engineering — have significant roles in the research.

Chakrabarti works in the areas of low-power embedded systems and algorithm-architecture co-design of signal processing and communication systems. Ogras and Brunhaver work on design and optimization of heterogeneous architectures.

If successful, the project will essentially provide master plans for designing, building and maximizing the use of computer chips (small wafers of semiconductor material embedded with integrated electronic circuitry) that are capable of simultaneously processing complex computations for a variety of diverse programs.

“We are going to go all the way from providing ideas for making it easier to figure out how this new kind of chip should be assembled to providing the software to help put it together,” Bliss explains.

“Then we will give you the software tools and analysis tools to help you program these chips to run multiple applications, including some tools that run in real-time inside the chip,” he adds.

Moreover, the team hopes to embed intelligent and machine learning functionality into the chips.

“This enables the chip itself to learn, based on how it is being used, so that it can operate more efficiently in the way it is running various applications,” Bliss says.

At least a dozen ASU engineering graduate students and postdoctoral fellows will get valuable experience working on aspects of the research project aimed at developing the next generation of heterogeneous architectures for multi-application systems. Pictured with Professor Daniel Bliss in his lab are (left to right) Richard Gutierrez, Postdoctoral Fellow Alex Chiriyath and electrical engineering doctoral student Hanguang Yu. Photographer: Marco-Alexis Chaira/ASU

Beyond those enhanced capabilities, processors using these chips will be capable of running extensive, sophisticated computations with significantly less power than they require with current technologies. Operations that now require hundreds of watts of electrical power might need only several watts.

Other research teams working under the DARPA initiative are aiming to make advances by integrating different materials into computer processors, by better understanding and enhancing the underlying physics involved in processing and by developing novel microelectronics designs and potential new applications.

These efforts combined could alter the paradigms of how computer processing is done or even fundamentally change the technology used to do processing, Bliss says.

“Right now we have researchers who know certain things are theoretically possible to do, but they are saying ‘We can’t do this because it is either too complicated computationally, which then consumes too much power, or it is too difficult and expensive to implement,’” Bliss says.

The DARPA project offers the team “the chance to find ways to boost computational power by a couple orders of magnitude so we can do some of the things we dream of achieving,” he says.

Bliss’ project — for which the agency is providing $17 million in support over four years — will give him the opportunity to dive deeper into one of his main research pursuits: signal processing technologies and systems, which are the key parts of many kinds of sensor, monitoring and communications systems.

Unmanned autonomous systems, including unmanned aerial vehicles, are among the newer technologies that rely heavily on signal processing. But they present a challenge, Bliss says, because “they have limited energy availability, which limits capabilities given current computational systems.”

In addition to applying this technology to unmanned autonomous systems, DARPA has challenged Bliss’ team to develop tools that design and use heterogeneous computing processors for a broad range of signal processing applications.

“It will affect the technology that lives in cell phones, in your smartwatch, in your camera, the information systems in your car,” Bliss says, “and it could make all of this tech less expensive, more energy efficient and more powerful.”

The research promises to provide tools for boosting the capabilities of myriad types of communication, sensing and biomedical technologies and systems.

More robust computational ability should open the door to tech improvements that boost the performance of things like heart monitors and other health assessment devices, as well as radar systems such as those used in self-driving vehicles and security systems.

“What should come out of this are better processors for all kinds of things we use in our everyday lives,” Bliss says.